# Investigation of Spin-on Dopants and Curing Temperature Effect on Dopant Activation

Bhavink Patel<sup>1</sup>, Martin Saporito<sup>1</sup>, Runye Cui<sup>1</sup>, Khaled Malallah<sup>1</sup>, Mohammad Alsubaiei<sup>1</sup> & Wei Du<sup>1</sup>

<sup>1</sup> Department of Electrical Engineering and Physics, Wilkes University, Wilkes-Barre, PA USA

Correspondence: Wei Du, Department of Electrical Engineering and Physics, Wilkes University, Wilkes-Barre, PA USA. E-mail: wei.du@wilkes.edu

| Received: May 24, 2019   | Accepted: June 6, 2019                | Online Published: July 15, 2019 |

|--------------------------|---------------------------------------|---------------------------------|

| doi:10.5539/apr.v11n4p11 | URL: http://dx.doi.org/10.5539/apr.vl | l1n4p11                         |

# Abstract

Spin-on dopant technique has been investigated in the paper. The boron and phosphorus were used as p- and n-type dopant sources and were deposited on silicon substrates, followed by the baking process to evaporate the solvents from spin-on dopant layers. The standard drive-in process was applied to diffuse and activate the dopants. The curing temperature varied from 150 to 200 °C to investigate the temperature effect on dopant activation. It is suggested that for our selected spin-on dopant sources, the curing temperature and time of 175 °C and 60 minutes would lead to the best result of dopant activation during drive-in process, evidenced by the lowest sheet resistance, which was measured using four-point probe measurement method.

Keywords: spin-on dopant, curing temperature, dopant activation

## 1. Introduction

Silicon has been the miracle material for the electronics industry that drives the digital revolution. The rapid "Moore's law" miniaturization of device sizes has yielded an ever-increasing density of fast components integrated on Si chips, pushing down feature size close to its ultimate physical limits. At the same time, there has been a parallel effort to broaden the reach of Si technology by expanding its functionalities well beyond electronics. Si is now being increasingly investigated as a platform for building photonic devices (Soref & Lorenzo, 1986; Soref, 2008). The huge infrastructure of the global Si electronics industry is expected to benefit the fabrication of highly sophisticated Si photonic devices at the costs that are lower than those currently required for compound semiconductors. Furthermore, Si-based optoelectronic devices make possible the monolithic integration of photonic devices with high-speed Si electronics, thereby enabling an oncoming Si based optoelectronic revolution.

After years of assiduous pursuing, Si-based optoelectronic device has found wide applications in the fields of photodetector (Berencén et al., 2017), solar cell (Blakers et al., 2013), waveguide, modulator (Shibuya et al., 2019), etc. The Si industry demands doping techniques to precisely control the material electrical property. One conventional method is well established chemical vapor deposition (CVD), which however requires the use of furnace twice for pre-deposition and drive-in and could be expansive due to explosive source gas. The other widely used method is ion implantation, which involves the bombardment of Si with high-energy dopant ions that replace Si atoms in the lattice. This method offers excellent doping uniformity, however, the point defects and vacancies in the lattice introduced by bombardment process would degrade the material quality, and consequently deteriorate the device performance.

An alternative method is to use spin-on dopant (SOD), which spins a dopant-containing solution onto Si substrates, followed by the thermal curing and then the thermal diffusion steps (Teh et al., 1989; Martínez et al., 2016; Hoarfrost et al., 2013). This method offers a number of advantages over conventional methods that were abovementioned: i) Room temperature spinning process and only one time furnace used for drive-in enable the SOD technique simple and rapid; ii) The SOD sources feature relative low-cost and safe, and therefore the monitor toxic gas can be eliminated; and iii) abandon of high energy dopant ions allow for SOD technique being nondestructive. However, the dopant activation is an issue which affects the effective doping concentration, which has been pointed out but is less studied so far. In this work, the SOD method for Si doping is investigated. Particularly, the curing temperature effect on dopant activation is studied, which suggests the optimized parameters to achieve the effective doping.

### 2. Experimental Method

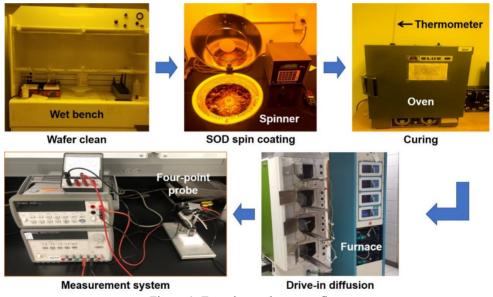

The Si substrates (100, 750- $\mu$ m-thick, 2-inch-diameter, single-side polished) used in the work are n-type (or p-type) doped with bulk resistivity of 1-5  $\Omega$ ·cm. The wafers were chemically cleaned using standard RCA-1 process, and then the native oxide layer was etched using 6:1 buffered oxide etchant (BOE). The cleaning process was completed after DI water rinsing and drying.

The Filmtronics SOD B155 and P509 were used as p-type and n-type dopants, respectively. The spinning was done at 4,000 rpm (10,000 rpm/sec acceleration) for 40 seconds at room temperature using a photoresist spinner. The coated wafers were than cured in an exhaust oven for solvent evaporation. The curing temperature and time range from 150 to 200 °C and 20 to 60 minutes, respectively, aiming to investigate the curing temperature effect on dopant activation. The drive-in diffusion was carried out in a furnace at 1000 °C for 60 minutes. During the process, the non-oxidizing ambient was created to avoid the surface oxidation, which was achieved by flowing high pure nitrogen gas into the furnace tube at a flow rate of 5 slm.

After the doping process, the sheet resistance was then determined by using four-point probe measurement method: the current (I) passing through the outer probes and the induced voltage drop (V) across the inner probes were measured and the sheet resistance ( $\rho_{\Box}$ ) is calculated using:

$$\rho_{\Box}(\Omega/\Box) = \frac{\pi}{\ln(2)} \times \frac{V}{I} \tag{1}$$

The experimental process flow is shown in Figure 1.

Figure 1. Experimental process flow

#### 3. Results and Discussions

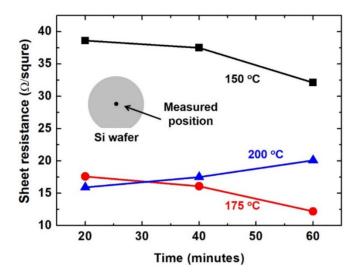

The p-type boron SOD on n-type Si substrate was firstly investigated. The sheet resistance was measure at the center of each wafer, as shown in Fig. 2. At curing temperature of 150 °C, as the curing time increases from 20 to 60 minutes, the sheet resistance decreases from 38.6 to 32.1  $\Omega/\Box$ . This is due to that the increases curing time could lead to more activated dopants during drive-in diffusion process. As curing time continue increasing (data not shown here), the sheet resistance does not further decrease, showing the saturation of activated dopants.

At curing temperature of 175 °C, as the curing time increases from 20 to 60 minutes, the similar sheet resistance decrease was observed, ranging from 17.6 to 12.2  $\Omega/\Box$ . Compared with those at 150 °C, the much lower sheet resistance was obtained. This implies that curing temperature plays an important role for dopant activation: the higher curing temperature could effectively activate more boron dopants. The sheet resistance at curing temperature of 175 °C is almost one third of its value at 150 °C (40 minutes curing time). As curing time further increases, the similar saturation of activated dopants was observed.

The curing temperature of 200 °C was investigated in the same way. With 20 minutes curing time, the sheet resistance of 15.9  $\Omega/\Box$  was obtained, which is lower than those at 150 and 175 °C at the same time. However, as curing time increases, the sheet resistance increases as well. This can be interpreted as following: curing temperature of 200 °C for 20 minutes has already sufficiently led to dopant activation during the later drive-in process. The increased curing time results in over thermal budget, which is consequently attributed to the increase of deactivated dopants. As curing time increased to 60 minutes, the sheet resistance increases to 20.1  $\Omega/\Box$ , which is higher than that at 175 °C.

Figure 2. Sheet resistance measured at the center of each wafer (see black dot in the inset), which is determined by four-point probe measurement method. The best curing parameters are 175 °C for 60 minutes

It can be clearly seen that the curing temperature is not the higher the better, as effective doping may be reduced due to over thermal budget. On the other hand, the curing temperature and time can be tuned to achieve the desired sheet resistance, as appropriate higher temperature could compensate the shorter curing time to achieve the same result. For example, the sheet resistance at 175 °C for 40 minutes is very close to that at 200 °C for 20 minutes (16.1 vs 15.9  $\Omega/\Box$ ).

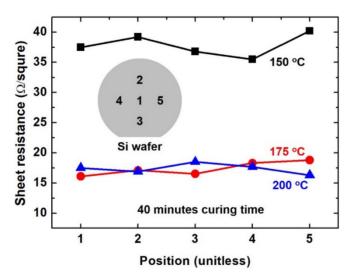

Figure 3. Sheet resistance measured at 5 positions to illustrate the doping uniformity. The distance from position 2-5 to 1 is 1.27 cm (half inch)

The increase of wafer size is the trend for industry, and therefore the doping uniformity is essential. To investigate the doping uniformity, beyond center position (position 1), 4 other positions, labelled as 2-5, were measured. The distance between these points to position 1 is 1.27 cm (half inch). The typical sheet resistance under 40 minutes curing time is shown in Fig. 3. At 150 °C, the sheet resistance varies from 35.5 to 40.2  $\Omega/\Box$ , exhibiting the uniformity degree of 90.1%. At 175 and 200 °C, the sheet resistance ranges from 16.1 to 18.8  $\Omega/\Box$ , and 16.3 to 18.5  $\Omega/\Box$ , featuring the uniformity degree of 86.7% and 90.4%, respectively. The uniformity shows almost independent of curing temperature, indicating the reliable of SOD technique.

It is worth to point out that the wafers we used are 2-inch in diameter, which is relatively small size mainly for experimental purpose. Theoretically, the larger size wafer would feature much better uniformity degree compared to small size wafer. Therefore, for the 8- or 12-inch wafers in current industry, the higher average uniformity of  $\sim$ 95% can be expected.

The curing condition of 175 °C for 60 minutes was then applied to n-type phosphorus SOD (Filmtronics P509) on p-type Si substrate. All other process flow is exactly the same as abovementioned. The measured sheet resistance is summarized in Table 1.

Table. 1 Sheet resistance of phosphorus SOD on p-type Si

| Position                   | 1   | 2   | 3   | 4   | 5   |

|----------------------------|-----|-----|-----|-----|-----|

| Resistance $(\Omega/\Box)$ | 7.6 | 8.6 | 6.8 | 7.7 | 8.3 |

The positions are the same as shown in Fig. 3 inset. The measured sheet resistance is lower than p-type SOD on n-type Si substrate, which agrees with the instruction provided by Filmtronics. The uniformity degree is calculated as 82.1%, which is a bit lower than those shown in Fig. 3. We would like to point out that since the curing condition of 175 °C for 60 minutes was optimized for p-type SOD on n-type Si substrate, it may not be the best condition for n-type SOD on p-type Si substrate. This condition can be the starting point to explore the corresponding optimized curing condition. The investigation method introduced in the paper would be the guidance towards delivering such goal.

The junction depth  $(x_j)$  was further calculated, as following (Backenstoss, 2013):

$$x_j = \sqrt{4Dt \left[ ln \left( \frac{N_S}{N_B} \right) \right]} \tag{2}$$

where t is the drive-in diffusion time (3600 seconds);  $N_S$  is the effectively activated surface doping concentration, which can be estimated by measured sheet resistance;  $N_B$  is the background doping concentration, which is ~10<sup>15</sup> cm<sup>-3</sup> according to bulk resistivity of 1-5  $\Omega$ ·cm; and D is diffusivity, which is given by:

$$D = D_0 e^{(-E/kT)} \tag{3}$$

where k is Boltzmann's constant; T is absolute temperature;  $D_0$  is a constant and E is activation energy. For boron dopant, the values of  $D_0$  and E are 10.5 cm<sup>2</sup>/sec and 3.69 eV, respectively. The  $x_j$  is summarized in Table 2.

Table 2. Junction depth at different curing conditions

|                  | Junction depth (µm)   |      |                       | Effective surface concentration (cm <sup>-3</sup> ) |         |         |

|------------------|-----------------------|------|-----------------------|-----------------------------------------------------|---------|---------|

| Temperature (°C) | Curing time (minutes) |      | Curing time (minutes) |                                                     |         |         |

|                  | 20                    | 40   | 60                    | 20                                                  | 40      | 60      |

| 150              | 0.99                  | 1.00 | 1.00                  | 1.16E20                                             | 1.20E20 | 1.44E20 |

| 175              | 1.03                  | 1.04 | 1.06                  | 2.90E20                                             | 3.25E20 | 4.70E20 |

| 200              | 1.04                  | 1.03 | 1.03                  | 3.30E20                                             | 2.90E20 | 2.48E20 |

From Table 2, it can be seen that the junction depth only shows slight increase as the curing temperature increases from 150 to 200 °C, which is ~1.0  $\mu$ m. The curing time also has less effect on junction depth. On the other hand, the effective surface doping concentration shows clear increase as temperature increases. For instance, for 20 minutes curing time, the effective surface concentration is almost doubled as temperature increases from 150 to 200 °C. Note that at 200 °C, as curing time increases from 20 to 60 minutes, the effective surface concentration reduces ~24.8%, which is consistent with our previous analysis, i.e., the increase of deactivated dopants at higher curing temperature with longer curing time.

## 4. Conclusion

In this work, the SOD technique was investigated on Si substrate. The curing temperature effect on dopant activation was disclosed. The optimized curing condition, i.e., 175 °C for 60 minutes was determined for p-type boron SOD on n-type Si substrate, leading to the sheet resistance, junction depth, and effective surface doping concentration of 12.2  $\Omega/\Box$ , 1.06 µm, and 4.70E20 cm<sup>-3</sup>, respectively. Higher curing temperature and longer curing time could result in the increase of deactivated dopants during the drive-in process. The investigation method introduced in this paper is a guidance to explore the optimized curing condition for other dopant/material systems.

## Acknowledgments

The work was supported by the Provost's Research & Scholarship Fund at Wilkes University. We also thank Mrs. Maria Bianco from Department of Chemistry and Prof. Robert Taylor from Department of Electrical Engineering and Physics at Wilkes University for their effort in chemical preparation and students' guidance, respectively.

## References

- Backenstoss, G. (1958). Evaluation of the surface concentration of diffused layers in silicon. *Bell System Technical Journal*, *37*(3), 699-710. https://doi.org/10.1002/j.1538-7305.1958.tb03882.x

- Berencén, Y., Prucnal, S., Liu, F., Skorupa, I., Hübner, R., Rebohle, L., ... Skorupa, W. (2017). Room-temperature short-wavelength infrared Si photodetector. *Scientific reports*, 7, 43688. https://doi.org/10.1038/srep43688

- Blakers, A., Zin, N., McIntosh, K. R., & Fong, K. (2013). High efficiency silicon solar cells. *Energy Procedia*, 33, 1-10. https://doi.org/10.1016/j.egypro.2013.05.033

- Hoarfrost, M. L., Takei, K., Ho, V., Heitsch, A., Trefonas, P., Javey, A., & Segalman, R. A. (2013). Spin-on organic polymer dopants for silicon. *The Journal of Physical Chemistry Letters*, 4(21), 3741-3746. https://doi.org/10.1021/jz4019095

- Martínez, J., Moreno, M., Rosales, P., Torres, A., Ambrosio, R., & Murias, D. (2016). Study of the spin on dopant technique as alternative for the fabrication of c-Si solar cells. 2016 IEEE 43rd Photovoltaic Specialists Conference (PVSC). https://doi.org/10.1109/PVSC.2016.7750090

- Shibuya, K., Atsumi, Y., Yoshida, T., Sakakibara, Y., Mori, M., & Sawa, A. (2019). Silicon waveguide optical modulator driven by metal-insulator transition of vanadium dioxide cladding layer. *Optics express*, 27(4), 4147-4156. https://doi.org/10.1364/OE.27.004147

- Soref, R. A., (2008). Towards Silicon-based Longwave Integrated Optoelectronics (LIO). SPIE Photonic West, Invited paper 6898-5, Silicon Photonics III. https://doi.org/10.1117/12.765459

- Soref, R., & Larenzo, J. (1986). All-silicon active and passive guided-wave components for  $\lambda$ = 1.3 and 1.6 µm. *IEEE Journal of Quantum Electronics*, 22(6), 873-879. https://doi.org/10.1109/JQE.1986.1073057

- Teh, S. T., & Chuah, D. G. S. (1989). Diffusion profile of spin-on dopant in silicon substrate. Solar energy materials, 19(3-5), 237-247. https://doi.org/10.1016/0165-1633(89)90009-9

# Copyrights

Copyright for this article is retained by the author(s), with first publication rights granted to the journal.

This is an open-access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/4.0/).